- 您现在的位置:买卖IC网 > Sheet目录3822 > PIC18F4525-I/ML (Microchip Technology)IC MCU FLASH 24KX16 44QFN

1996 Microchip Technology Inc.

DS30412C-page 125

PIC17C4X

IORWF

Inclusive OR WREG with f

Syntax:

[

label ]

IORWF

f,d

Operands:

0

≤ f ≤ 255

d

∈ [0,1]

Operation:

(WREG) .OR. (f)

→ (dest)

Status Affected:

Z

Encoding:

0000

100d

ffff

Description:

Inclusive OR WREG with register 'f'. If

'd' is 0 the result is placed in WREG. If

'd' is 1 the result is placed back in regis-

ter 'f'.

Words:

1

Cycles:

1

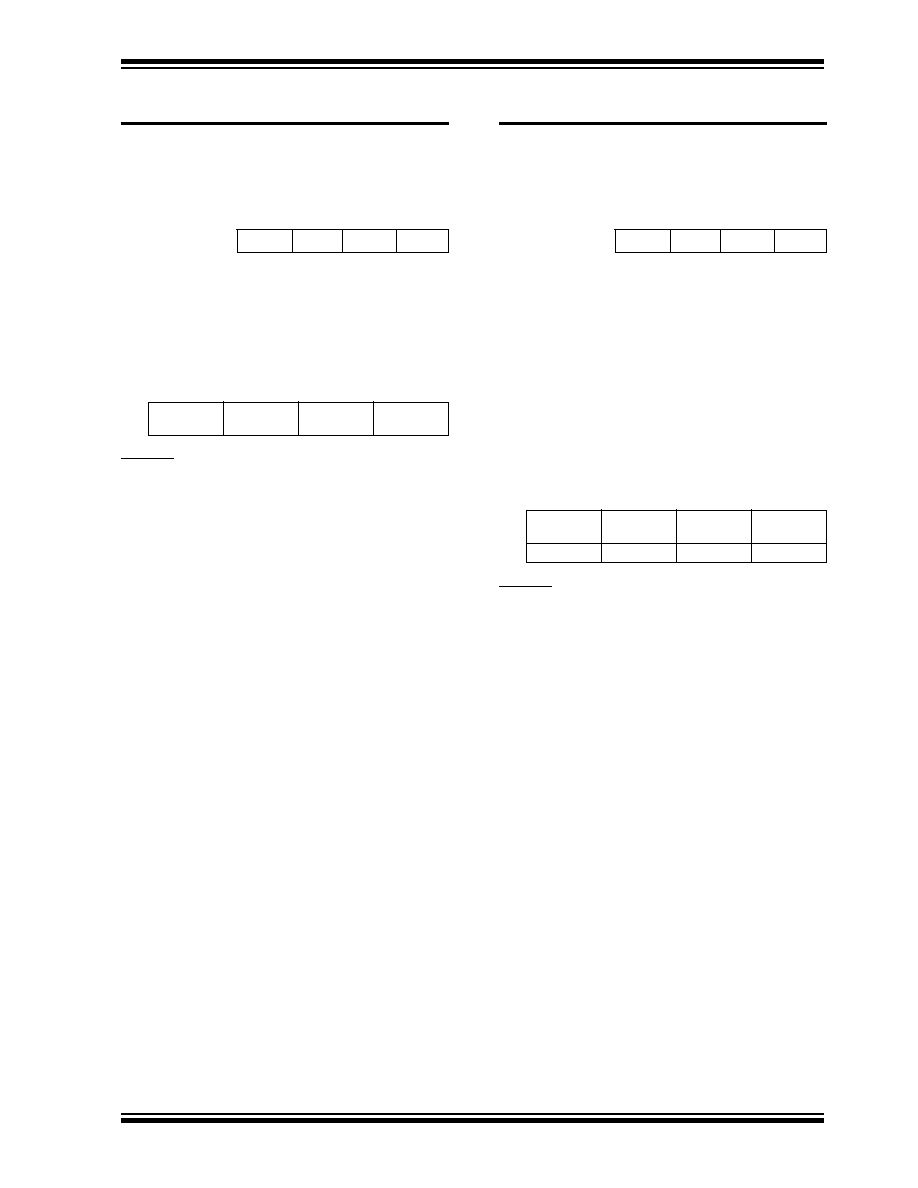

Q Cycle Activity:

Q1

Q2

Q3

Q4

Decode

Read

register 'f'

Execute

Write to

destination

Example:

IORWF

RESULT, 0

Before Instruction

RESULT =

0x13

WREG

=

0x91

After Instruction

RESULT =

0x13

WREG

=

0x93

LCALL

Long Call

Syntax:

[

label ]

LCALL

k

Operands:

0

≤ k ≤ 255

Operation:

PC + 1

→ TOS;

k

→ PCL, (PCLATH) → PCH

Status Affected:

None

Encoding:

1011

0111

kkkk

Description:

LCALL

allows an unconditional subrou-

tine call to anywhere within the 64k pro-

gram memory space.

First, the return address (PC + 1) is

pushed onto the stack. A 16-bit desti-

nation address is then loaded into the

program counter. The lower 8-bits of

the destination address is embedded in

the instruction. The upper 8-bits of PC

is loaded from PC high holding latch,

PCLATH.

Words:

1

Cycles:

2

Q Cycle Activity:

Q1

Q2

Q3

Q4

Decode

Read

literal 'k'

Execute

Write

register PCL

Forced NOP

NOP

Execute

NOP

Example:

MOVLW

HIGH(SUBROUTINE)

MOVPF

WREG, PCLATH

LCALL

LOW(SUBROUTINE)

Before Instruction

SUBROUTINE

=

16-bit Address

PC

=

?

After Instruction

PC

=

Address (SUBROUTINE)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC30F2023-30I/ML

IC DSPIC MCU/DSP 12K 44QFN

PIC16LF767-I/ML

IC PIC MCU FLASH 8KX14 28QFN

PIC18LF2320-I/SO

IC MCU FLASH 4KX16 EEPROM 28SOIC

PIC18F4458-I/ML

IC PIC MCU FLASH 12KX16 44QFN

DSPIC33FJ64GP706A-I/PT

IC DSPIC MCU/DSP 64K 64-TQFP

PIC16F874-20/P

IC MCU FLASH 4KX14 EE 40DIP

DSPIC33FJ64GP706-I/PT

IC DSPIC MCU/DSP 64K 64TQFP

PIC24HJ128GP210-I/PT

IC PIC MCU FLASH 128KB 100TQFP

相关代理商/技术参数

PIC18F4525-I/P

功能描述:8位微控制器 -MCU 48KB 3968 RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4525-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4525 DIP40

PIC18F4525-I/PT

功能描述:8位微控制器 -MCU 48KB 3968 RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4525-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4525 TQFP44

PIC18F4525T-I/ML

功能描述:8位微控制器 -MCU 48KB 3968 RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4525T-I/PT

功能描述:8位微控制器 -MCU 48KB 3968 RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F452-BL

制造商:POWERLITE SYSTEMS 功能描述:BOOTLOADER PIC18F452 FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:BOOTLOADER, PIC18F452, FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:BOOTLOADER, PIC18F452, FOR FLASHLAB, Silicon Manufacturer:Powerlite Systems, Cor 制造商:POWERLITE SYSTEMS 功能描述:PIC18F452 W/ BOOTLOADER, FOR FLASHLAB, Silicon Manufacturer:Powerlite Systems, Core Architecture:PIC, Core Sub-Architecture:PIC18F, Kit Contents:Board , RoHS Compliant: Yes

PIC18F452-E/L

功能描述:8位微控制器 -MCU 32KB 1536 RAM 34I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT